PATENT ABSTRACTS OF JAPAN

(11)Publication number : 2002-237468 (43)Date of publication of application : 23.08.2002

| (51)Int.Cl.                          | H01L 21/28<br>H01L 21/02<br>H01L 21/3063<br>H01L 21/316 |                                |    |

|--------------------------------------|---------------------------------------------------------|--------------------------------|----|

| (21)Application number : 2001-034528 | (71)Applicant :                                         | FUJIKURA LTD                   |    |

| (22)Date of filing : 09.02.2001      | (72)Inventor :                                          | TAKIZAWA ISAO<br>SATOU AKINOBU | •• |

|                                      |                                                         | SUEMASU TATSUO                 |    |

|                                      |                                                         | ITOI KAZUHISA                  |    |

(54) METHOD OF FORMING ELECTRODE PASSED THROUGH SUBSTRATE, AND SUBSTRATE HAVING THROUGH ELECTRODE (57)Abstract:

PROBLEM TO BE SOLVED: To form a through electrode passed through a silicon substrate and having a high aspect ratio.

SOLUTION: A through hole 12 having a high aspect ratio is formed by a photo-excited electrolytic polishing process in a silicon substrate 11. The inner wall of the through hole 12 is subjected to oxidation to form an oxide film 21 as an insulating layer. Then a metal 23 is filled into the through hole 12 by a melted metal refilling process to form a through electrode (23). The through electrode 12 having a high aspect ratio can be easily formed in the substrate 11, and thus there can be easily achieved a semiconductor package having, e.g. stacked silicon IC chips.

# EGAL STATUS13.07.2001[Date of request for examination]13.07.2001[Date of sending the examiner's decision of rejection]Image: Sending the examiner's decision of rejection][Kind of final disposal of application other than the examiner's decision of rejection or application converted registration]Image: Sending the examiner's decision of rejection][Date of final disposal for application]Image: Sending the examiner's decision of rejection][Patent number]3599325[Date of registration]24.09.2004[Number of appeal against examiner's decision of rejection]Image: Sending the examiner's decision of rejection][Date of requesting appeal against examiner's decision of rejection]Image: Sending the examiner's decision of rejection]

[Date of extinction of right]

Searching MAJ

2006/11/10

THIS PAGE BLANK (USPTO)

A

\* NOTICES \*

## JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely. 2.\*\*\*\* shows the word which can not be translated.

| 3.In the drawings, any words are | e not translated. | • |  |

|----------------------------------|-------------------|---|--|

|                                  |                   |   |  |

|                                  |                   |   |  |

| CLAIMS                           | · · ·             |   |  |

#### ······

#### [Claim(s)]

[Claim 1] The penetration electrode formation approach of the substrate which is the penetration electrode formation approach which forms a penetration electrode in substrates, such as a silicon substrate, oxidizes the wall of this through tube, forms [ the through tube of a high aspect ratio is formed in a substrate, and ] the oxide film as an insulating layer with optical-pumping electrolytic polishing, and is characterized by being filled up with a metal by the molten-metal backfilling method subsequently to said through tube.

[Claim 2] The penetration electrode formation approach of the substrate according to claim 1 characterized by having the process which faces forming the oxide film as an insulating layer in a through tube wall, once removes the oxide film formed in the through tube wall, oxidizes a through tube wall again after that, and forms an oxide film once [ at least ].

[Claim 3] The penetration electrode formation approach of the substrate according to claim 1 characterized by facing forming the oxide film as an insulating layer in a through tube wall, carrying out high-concentration impurity diffusion to a through tube wall, and forming an impurity diffused layer in the outside of an oxide film.

[Claim 4] It is the substrate which it is substrates, such as silicon which has a penetration electrode, and said penetration electrode is formed by optical-pumping electrolytic polishing, consists of a through tube which has an oxide film in a wall, and a metal with which said through tube was filled up, and has the penetration electrode characterized by forming at least one place of said penetration electrode in said substrate.

#### [Translation done.]

#### JP,2002-237468,A [DETAILED DESCRIPTION]

\* NOTICES \*

# JPO and NCIPI are not responsible for any damages caused by the use of this translation.

This document has been translated by computer. So the translation may not reflect the original precisely.

\*\*\*\* shows the word which can not be translated.

In the drawings, any words are not translated.

#### DETAILED DESCRIPTION

#### [Detailed Description of the Invention]

#### [0001]

[The technical field belonging to invention] The penetration electrode formation approach that this invention forms a penetration electrode in substrates, such as a silicon substrate, Like [ in the case of forming a penetration electrode in the silicon substrate at the time of carrying out the slaminating of the silicon IC chip, and carrying out high density assembly, concerning the device using the substrate which has at least one penetration electrode formed by the approach concerned, and the substrate concerned, ] When you need the penetration electrode of a high aspect ratio, it relates with various devices, such as the penetration electrode formation approach of a suitably applicable substrate, and an electron device which carried out substrates, such as silicon which has a penetration electrode, and the substrate concerned at the base, an optical device. [0002]

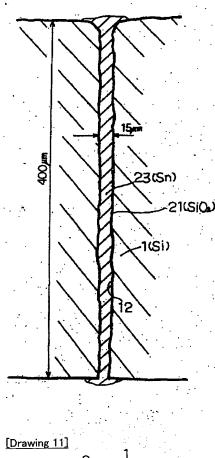

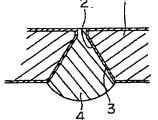

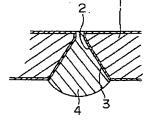

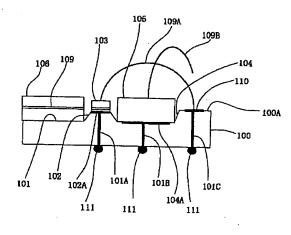

[Description of the Prior Art] For example, as an approach of forming the penetration electrode which penetrates a front flesh side to a silicon substrate, after performing anisotropic etching, an oxide film is formed and the method of taking a flow with solder is proposed. In this case, as shown in <u>drawing 11</u>, the through tube 2 formed in the silicon substrate 1 by anisotropic etching becomes what has a big area of opening to substrate thickness. 3 shows an oxide film and 4 shows solder. moreover, ICP-RIE (Inductively Coupled Plasma-Reactive Ion Etching) which forms a penetration electrode in a silicon substrate — the approach of forming a through tube using law, and carrying out metal plating of the through tube wall, and forming a penetration electrode is also proposed.

[0003] On the other hand, optical-pumping electrolytic polishing (J. Electrochem.Soc., Vol.137, No.2, 653 to pp659 reference) is known as a technique which forms the through tube of a high aspect ratio (hole opening aspect product to the depth) in a silicon substrate. The detail of this optical-pumping electrolytic polishing is mentioned later.

#### [0004]

[Problem(s) to be Solved by the Invention] By the approach of of the above-mentioned conventional anisotropic etching and solder, since an etching configuration has constraint and the area of opening of the through tube to the thickness of a silicon substrate 1 becomes large, the penetration electrode of a high aspect ratio cannot be formed and it is not fit for formation of the penetration electrode to the silicon substrate in the case of performing high density assembly of a silicon IC chip.

[0005] moreover, since it is [ in a through tube ] deep and the until penetration of reactant gas or the plating liquid cannot be carried out by the approach of ICP-RIE and metal plating, it is difficult too to form the penetration electrode of a high aspect ratio.

[0006] Moreover, in the configuration of the through tube formed with optical-pumping electrolytic polishing, since a side branch etc. arises, a flat wall surface is not obtained.

[0007] This invention was made in view of the above-mentioned situation, and it is possible to form the penetration electrode of a high aspect ratio, and it aims at offering the substrate which has the penetration electrode formation approach and penetration electrode of a substrate which can make flat the wall of a through tube with which a penetration electrode is formed. [0008]

[Means for Solving the Problem] This invention which solves the above-mentioned technical problem is the penetration electrode formation approach which forms a penetration electrode in substrates, such as a silicon substrate, it forms the through tube of a high aspect ratio in a substrate, oxidizes the wall of this through tube, forms the oxide film as an insulating layer, and, subsequently to said through tube, is characterized by being filled up with a metal by the molten-metal backfilling method.

[0009] Claim 2 is characterized by facing forming the oxide film as an insulating layer in a through tube wall, once removing the oxide film formed in the through tube wall, oxidizing a through tube wall again after that, and forming an oxide film in the penetration electrode formation approach of the substrate of claim 1.

[0010] Claim 3 is characterized by facing forming the oxide film as an insulating layer in a through tube wall, carrying out high-concentration impurity diffusion to a through tube wall, and forming an impurity diffused layer in the outside of an oxide film in the penetration electrode formation approach of the substrate of claim 1.

[0011] Claims 4 are substrates, such as silicon which has a penetration electrode, said penetration electrode is formed by optical-pumping electrolytic polishing, and consists of a through tube which has an oxide film in a wall, and a metal with which said through tube was filled up, and said penetration electrode is characterized by the substrate which has the penetration electrode currently formed at least one place in said substrate. [0012]

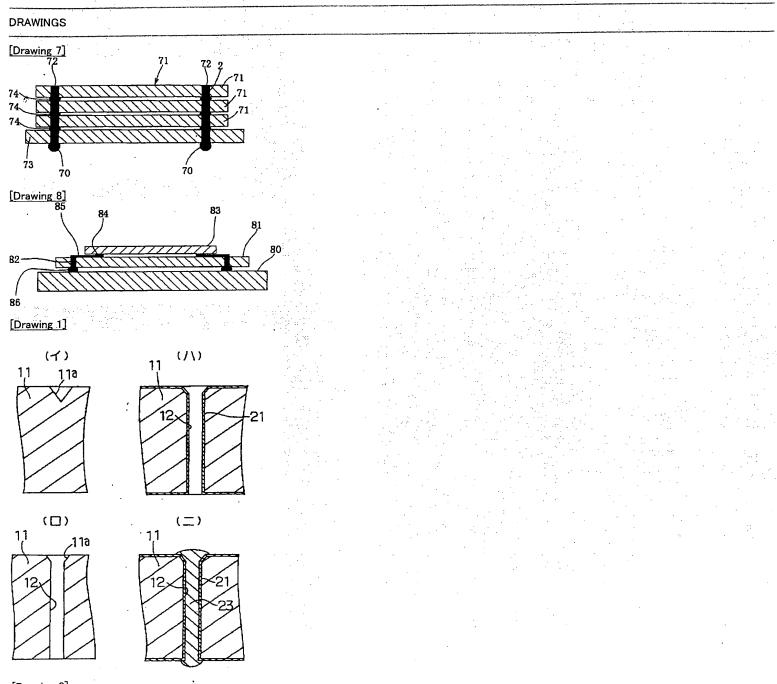

[Embodiment of the Invention] Hereafter, the gestalt of operation of this invention is explained with reference to drawing 1 - drawing 10. This operation gestalt assumes the case where a penetration electrode is formed in the silicon substrate at the time of carrying out the laminating for example, of the silicon IC chip, and carrying out high density assembly.

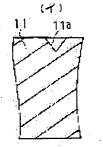

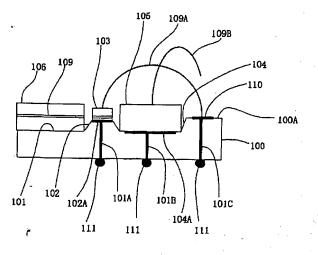

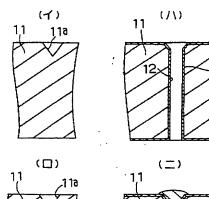

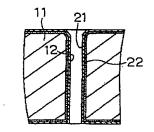

\*\* First, as shown in the <u>drawing 1</u> (\*\*), form V type hollow (this example is square drill-like hollow) 11a by the anisotropic etching which used etching reagents, such as KOH, for the silicon substrate 11.

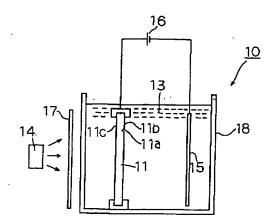

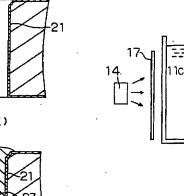

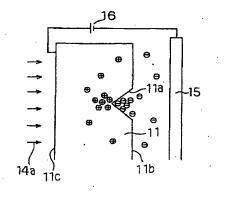

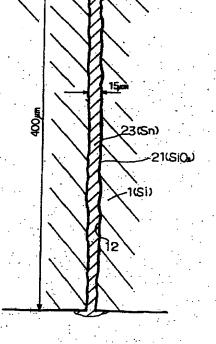

[0013] **\*\*** Subsequently to the location of V type hollow 11a of said silicon substrate 11, form a through tube 12 like <u>drawing 1</u> (b) with opticalpumping electrolytic polishing. It explains with reference to the optical-pumping electrolytic-polishing equipment 10 and <u>drawing 3</u> which showed the principle of formation of the through tube 12 by optical-pumping electrolytic polishing to <u>drawing 2</u>. The silicon substrate 11 of n mold which formed V type hollow 11a in surface 11b by KOH beforehand as mentioned above Being immersed in the electrolytic solution 13 which consists of an HF solution in a cell 18, and irradiating light (14 showing the light source) through the infrared filter 17 at rear-face 11c corresponding to said V type hollow 11a of this silicon substrate 11 If a current (16 shows DC power supply) is passed between said silicon substrates 11 and cathode electrodes 15 which were made into the anode plate, said V type hollow location of a silicon substrate 11 will be etched alternatively, and a through tube 12 will be formed in this V type hollow location. If optical 14a is irradiated at the rear face of the silicon substrate 2 of n mold as it is shown in <u>drawing 3</u>, when the principle etched alternatively is explained When a minority carrier (electron hole) is generated with the rear face of a silicon substrate 2 by excitation by the optical exposure and the minority carrier concentrates at the tip of V type hollow 11a of the shape of a square drill by the side of a front face Only the tip of V type hollow 11a is etched electrochemically, the etching advances, and a through tube 12 by this optical-pumping electrolytic polishing, for example in 50 degrees C and 2.5wt% HF etching reagent, it grinds in illuminance 6 mW/cm [ of light ]2, 0.1mA [ of force current ], and impression time amount 24 hours, for example, a through tube with a diameter [ of

#### JP,2002-237468,A [DETAILED DESCRIPTION]

#### 15 micrometers ] and a depth of 400 micrometers is formed.

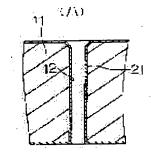

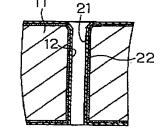

[0014] Subsequently, as it oxidizes and the wall of said through tube 12 is shown in <u>drawing 1</u> (Ha), the oxide film 21 as an insulating layer is formed. Formation of an oxide film 21 can be formed for example, by the oxidizing [ thermally ] method. As a concrete example of thermal oxidation, it puts to the wet ambient atmosphere which poured the steam of 1100 degrees C and 2000 cc/min. for 3 hours, for example, and an oxide film 21 is formed. [0015] In addition, since a side branch etc. produces the wall of a through tube established with optical-pumping electrolytic polishing and a flat internal surface is not obtained when forming an oxide film 21 as an insulating layer, it is desirable to remove the once formed oxide film 21, to oxidize again, and to form an oxide film. Thereby, flattening of the internal surface of a through tube 12 can be carried out, and a good penetration electrode can be formed. In addition, oxide film removal can be performed by etching the oxide film in a through tube 12 alternatively by BOE (buffered fluoric acid) etc. Moreover, if the process of said oxide-film removal and oxide-film reconstitution is repeated two or more times depending on the case, flattening of the internal surface of a through tube 12 can be carried out further.

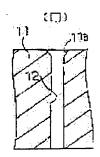

[0016] Moreover, in case an oxide film is formed, high-concentration impurity diffusion can be performed and the layer (impurity diffusion tub) formed of it can be used as a shielding layer. 22 shows the impurity diffused layer formed in <u>drawing 4</u> by impurity diffusion. A noise can be controlled by formation of a shielding layer. It is good to diffuse the matter which forms p type layers, such as boron, as an impurity to diffuse, for example in the case of n mold silicon substrate. Moreover, impurity diffusion can be performed with a thermal diffusion method. According to this thermal diffusion method, since formation of the insulating layer on an impurity diffused layer 22 (oxide film 21) can also be performed to coincidence, it is efficient. If a drive-in is performed as a concrete example of the impurity diffusion by thermal diffusion for 1,100 degrees C, a wet oxidizing atmosphere, and 3 hours after carrying out deposition of the boron glass by nitrogen-gas-atmosphere mind for 950 degrees C and 1 hour using the source of impure of solid phase or a gaseous phase when diffusing boron, for example in n mold silicon substrate, an about 2-micrometer high concentration P++ layer (impurity diffused layer 22) will be formed, for example.

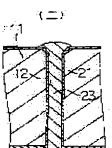

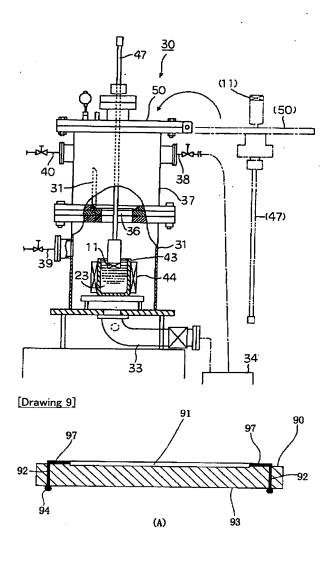

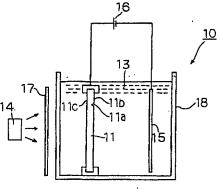

[0017] Subsequently, by the molten-metal backfilling method, as shown in <u>drawing 1</u> (d), it is filled up with a metal 23 in a through tube 12. A moltenmetal backfilling method is the approach of filling up with a metal detailed space, such as micropore formed in the silicon substrate (work piece) used as a processed object. First, decompress the ambient pressure of the work piece which it is going to fill up with a metal, and, subsequently the reduced pressure condition has been maintained. It is the approach characterized by inserting said work piece in molten metal, pressurizing the ambient pressure of said molten metal subsequently, filling up said space with molten metal according to the ambient pressure difference before and behind metal insertion, pulling up a work piece from a molten-metal tub, and subsequently cooling it. Here, although it is good for the eutectic solder of an indium (In), tin (Sn), or golden-tin etc. to have the comparatively low melting point, and to use a metal with low vapor pressure as a metal with which it is filled up, it is not limited to especially them. It is immersed in 300-degree C melting tin by using as a work piece the silicon substrate 11 which used molten-metal restoration equipment 30 like <u>drawing 5</u>, for example, for example, opened the through tube 12 in the reduced pressure ambient atmosphere of 10-3Pa (pascal) extent as a concrete example of this molten-metal backfilling, for example, you make it filled up with tin in the through tube 12 of the high aspect ratio in returning an ambient atmosphere to the bottom of atmospheric pressure after that.

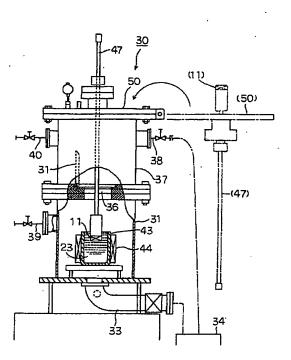

[0018] Said molten-metal restoration equipment 30 had the vacuum chamber 31 which has arranged the molten-metal tub 43 with heater 44, and the vacuum chamber 37 for buffers which is open for free passage by the opening 36 which can be opened and closed by the shutter 35 to this, and the arm 47 for work-piece immobilization which grasps a silicon substrate 11 is attached in the lid 50. It connects with vacuum pump equipment 34 through the siphon 33 or the siphon 38 for vacuum rough length, and both the chambers 31 and 37 are connected to the nitrogen gas cylinder of illustration abbreviation through the nitrogen installation tubing 39 and 40.

[0019] Explanation of the work habits which fill up a metal with above metal restoration equipment 30 into the through tube 12 of a silicon substrate 11 vacuum-rough-lengthens the vacuum chamber 37 interior for buffers with vacuum pump equipment 34, where the silicon substrate 11 which closed the lid 50 and was grasped with the arm 47 for work-piece immobilization is located in the vacuum chamber 37 for buffers. Subsequently, a shutter 35 is opened (in addition, the vacuum chamber 31 is decompressed previously). Subsequently, with vacuum-pump equipment 34, vacuum suction of the interior of the vacuum chamber 11 and the vacuum chamber 17 for buffers is carried out, and it decompresses to about 10-2 to 10 - 3Pa of vaccum pressure. Subsequently, it heats at a heater 44, melting of the metal in the molten-metal tub 43 is carried out, and a silicon substrate 11 is inserted into molten metal 23. After a silicon substrate 11 reaches the same temperature as molten metal 23, the nitrogen from a nitrogen gas cylinder is introduced in the vacuum chamber 11 and the vacuum chamber 17 for buffers, and the interior is pressurized to two to 5x105Pa (2 - 5 kgf/cm2) extent. This pressurization is filled up with molten metal 23 in the through tube 12 which is a high aspect ratio. Then, a silicon substrate 11 is pulled up from the molten-metal tub 43, it takes out besides the vacuum chamber 31, and air cooling is carried out at a room temperature. Thereby, the metal restoration activity to the through tube 12 of a silicon substrate 11 is completed.

[0020] In addition, as an approach of forming an insulating layer (oxide film) in the internal surface of a through tube 12, not only the above-mentioned oxidizing [ thermally ] method but forming under a low temperature service by the liquid phase of for example, the coating liquid for SiO2 system coat formation etc. is considered. Since this approach does not have the effect by heat on them when the circuit etc. is already formed on the silicon substrate 11, it becomes advantageous.

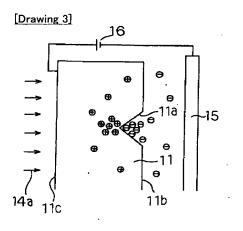

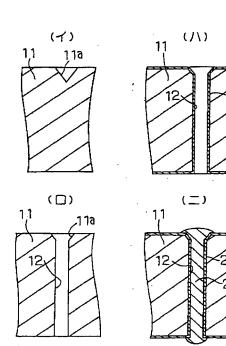

[0021] This invention applies and is suitable for the laminating high density assembly (three-dimension mounting) of a silicon IC chip. <u>Drawing 7</u> is the cross-sectional view showing the layered product of a silicon IC chip (silicon substrate). 71 in drawing is the silicon IC chip with which two penetration electrodes 72 were formed by optical-pumping electrolytic polishing, and the three-sheet laminating in all of this silicon IC chip 71 is carried out in the up-and-down location on the base substrate 73. When the silicon IC chip 71 has the same circuit pattern cut down from the same wafer and looks at it from a wafer front face, the penetration electrode 72 and a circuit pattern (not shown) are formed in the same location in each chip, and these penetration electrodes 72 double a vertical edge, and are connected. The penetration electrode upper limit on the other party chip is connected with the solder bump 74 prepared in the \*\*\*\* bee and the electrode lower limit, and alignment connection of the penetration electrode 72 of these chips is made with the penetration electrode 72 formed in the base substrate 73 made from silicon. Consequently, the common electrode vich penetrates a base substrate and a silicon IC chip is formed, and the solder ball 70 of the lower limit of this common electrode is connected with the wiring circuit of the base substrate which is not illustrated. However, when carrying out a design which does not dare arrange the vertical location of a penetration electrode and the chip of another side through which it flows) of the chip upper part of another side. As mentioned above, it is possible to make the three-dimension IC device whose packaging density was accumulated on two or more layers and improved by [ which position how many sheets of that IC chip in an arbitration location, and makes superposition connection ] having formed the penetration electrode of a high aspect ratio. In addition, the number of penetration electrodes is not limited to two, but this [ its ] is the same also in

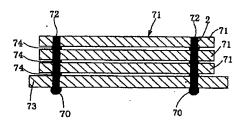

[0022] <u>Drawing 8</u> is other examples of this invention, and shows chip size mounting of IC chip using INTAPOZA. On those with INTAPOZA (silicon substrate) made from silicon which have two penetration electrodes 82 in which 81 in drawing was formed by optical-pumping electrolytic polishing, and this INTAPOZA, the IC chip 83 by which the face down was carried out is carried. The electrode 84 of IC chip front face is connected to the penetration electrode 82 through the conductive layer 85 on the front face of INTAPOZA, and the solder ball 86 formed in penetration electrode 82 lower limit is connected with the circuit pattern on a mother board (base substrate) 80 on this INTAPOZA inferior surface of tongue. Although connection with a mother board had much constraint and there was a limitation also in a wiring consistency by chip mounting using INTAPOZA conventionally, in this example, by forming two or more penetration electrodes of a high aspect ratio, constraint of a circuit pattern design of INTAPOZA decreases and mounting structure (or package structure) can be simplified. Furthermore, since silicon is used as a material of INTAPOZA, in case the adjustment of IC chip and a coefficient of thermal expansion becomes good and it mounts to a mother board as compared with the thing made from other ceramics, there is little thermal stress distortion which a chip receives, and since the heat transfer effectiveness of silicon is comparatively excellent, the advantage of being easy to miss the generating heat of a chip is acquired. Furthermore, since the silicon high precision

#### JP,2002-237468,A [DETAILED DESCRIPTION]

processing technology which has generally spread can be used, the advantage that the elaboration of a surface circuit pattern is possible is also acquired.

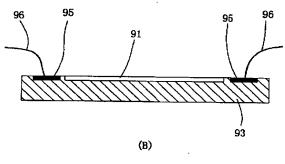

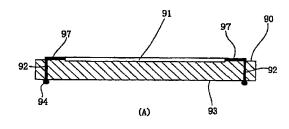

[0023] <u>Drawing 9</u> (A) is other examples of this invention, and shows the image sensors which have a penetration electrode. 91 are the photoelectric element area in the image-sensors chip 90 among drawing, and 92 is the penetration electrode of a high aspect ratio formed in the silicon substrate 93 by optical-pumping electrolytic polishing. This penetration electrode 92 is formed in a chip edge on the outside of the active region (photoelectric element area in which the optoelectric transducer was formed) 91 of image sensors, and the upper limit is connected to the active region 91 through the electrode layer on the front face of a chip. Moreover, the lower limit is connected with the circuit pattern on the front face of a mother board which is not illustrated through solder ball 94 grade.

[0024] <u>Drawing 9</u> (B) shows the image sensors of a wire connection type. In this Fig., image sensors formed in the same field as the component area of a chip the wire bond pad 95 with a comparatively big area which flows in this component area, and have connected it with the external leadframe etc. by the bonding wire 96. moreover, a gold streak (wire) — in order to mitigate the effect of the heat generated at the time of connection, the area of the image area which needs to carry out extent isolation and which is occupied on a chip front face from the above reason which a wire bond pad and image area have has constraint.

[0025] On the other hand, in this invention, since it connects with the photoelectric element area 91 through the conductive layer 97 and the penetration electrode upper limit of a high aspect ratio is connected with the exterior by the solder ball 94 of a penetration electrode lower limit, the wirebonding pad to the same field as image area becomes unnecessary. Therefore, since component area occupied to the chip area of image sensors can be enlarged, the component area of a large area is [ image sensors ] securable in a miniaturization or the chip of the limited magnitude. Moreover, since wirebonding is unnecessary, the surface mount to a base substrate becomes easy, and can measure reduction of a manufacturing cost in small [ of an image chip mounting substrate ], thin-shape-izing, and a list.

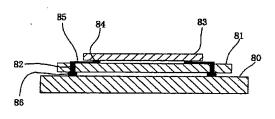

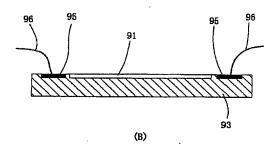

[0026] Drawing 10 is other examples of this invention, and shows the cross-sectional view of an optical circuit element (optical transmitter) in which the penetration electrode of a high aspect ratio was formed. Four penetration electrode 101A in which 100 in drawing was formed by optical-pumping electrolytic polishing, The platform made from silicon (silicon substrate) which has 101B and 101C (other one place is not shown) and by which precision processing was carried out, and 101 The projected part of the V groove which carries out positioning immobilization of the optical fiber 106, and the cross-section trapezoidal shape to which, as for 102, the top face to which one electrode surface of the surface mounting mold (laser diode) LD 103 is connected makes conductive layer 102A, 104 is a crevice of reverse trapezoidal shape where the concave pars basilaris ossis occipitalis connected to the single-sided electrode surface of PD105 for monitors (photo diode) makes conductive layer 104A, Conductive layer 102A. conductive layer 104A, and the flowing penetration electrodes 101A and 101B are formed in this projected part 102 and the lower part of this crevice 104, and the lower limit section of these penetration electrodes 101A and 101B is connected to them with the external circuit which does not form and illustrate a solder bump (pad). On the other hand, other two penetration electrode 101C (one place is not shown) is connected to two electrode pads 110 (one place is not shown) on platform surface 100A, and two bonding wires (gold streak) 109A and 109B derived from these electrode pad are connected to other single-sided electrode surfaces of LD103 and PD105. furthermore -- concrete -- a gold streak -- direct bonding of the 109A is carried out to the single-sided electrode on LD103 -- having -- a gold streak -- direct continuation of the 109B is connected with the extension section of conductive layer 104A plated on the platform rather than it is carried out to a component electrode. In the lower part of a platform 100, the surface mount of the lower limit of these penetration electrode is carried out to a mounting substrate through the solder ball 111 etc. [0027] Next, the optical axis is set so that it may be in agreement with the axial center 107 of an optical fiber 106, the outgoing radiation light of LD103 carries out incidence of the direction of a list of these light device to an optical fiber, and PD105 carries out the monitor of the LD output. According to this example, since each conductive layers 102A and 104A of the light corpuscle child lower part have flowed with the external circuit through the penetration electrodes 101A and 101B, formation of the circuit pattern on a platform front face is simplified. Moreover, as compared with connecting an external leadframe with a light corpuscle child from the electrode pad 110 in a platform, since it is only between light corpuscle children, wire length becomes short and it becomes easy to connect wire (gold streak) bonding. therefore, the optical whole device not only being miniaturized but a connection man day - \*\*\*\*\*\* - since things are made, there is an advantage to which product cost can be reduced. In addition, the configuration of the above-mentioned platform can be changed and a configuration which receives the external incident light from an optical fiber by PD for light-receiving, then an optical receiver can be constituted. Moreover, an optical fiber is made into two (it is v slot two), and an optical transceiver can be constituted, if a platform is processed and an optical transmitter and an optical receiver are fixed on the same platform. [0028] As explained above, this invention can form the penetration electrode of a high aspect ratio in various components, and since use of generalpurpose silicon high precision processing technology is possible, it can measure various components, the elaboration of a device, a miniaturization, and improvement in packaging density. Moreover, it is complicated, and since the process of the wire bond used as cost quantity etc. can be skipped, it also becomes possible to reduce product cost. In addition, although the case of this invention where a penetration electrode is formed in a silicon substrate is main, forming a penetration electrode in the substrate by materials other than silicon is also considered. [0029]

[Effect of the Invention] Since according to this invention the through tube of a high aspect ratio is formed in a substrate, for example with opticalpumping electrolytic polishing, the wall of this through tube is oxidized, the oxide film as an insulating layer is formed, it is filled up with a metal by the molten-metal backfilling method and a penetration electrode is formed subsequently to said through tube, the penetration electrode of a high aspect ratio can be obtained easily. It becomes easy for this to realize the semiconductor package and the optical device of the high density assembly which carried out the laminating for example, of the silicon IC chip etc.

[0030] If it reoxidates and an oxide film is formed once removing the oxide film formed in the through tube wall like claim 2, flattening of the through tube wall can be carried out, and a good penetration electrode can be formed.

[0031] If high-concentration impurity diffusion is carried out to a through tube wall and an impurity diffused layer is formed in the outside of an oxide film like claim 3, this impurity diffused layer can be used as a shielding layer, and it is effective in control of a noise.

[Translation done.]

\* NOTICES \*

#### JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely. 2.\*\*\*\* shows the word which can not be translated. 3.In the drawings, any words are not translated.

#### DESCRIPTION OF DRAWINGS

#### [Brief Description of the Drawings]

[Drawing 1] It is the mimetic diagram which divides the penetration electrode formation approach of the substrate of 1 operation gestalt of this invention into a process, and explains it, and the phase where (\*\*) formed the V type hollow in the silicon substrate, the phase in which (\*\*) opened the through tube with optical-pumping electrolytic polishing, the phase where (Ha) formed the oxide film in the through tube wall, and the phase which (d) filled up the through tube with the metal and formed the penetration electrode are shown.

[Drawing 2] In the penetration electrode formation approach of this invention operation gestalt, it is the mimetic diagram of the optical-pumping electrolytic-polishing equipment used for formation of a through tube.

[Drawing 3] It is drawing explaining the principle by which alternative etching is performed to a V type hollow with the above-mentioned opticalpumping electrolytic polishing.

[Drawing 4] It is the mimetic diagram showing the condition of having performed impurity diffusion and having formed the shielding layer (impurity diffusion) on the occasion of formation of the oxide film of drawing 1 (Ha).

[Drawing 5] a part of important section of the metal restoration equipment used for the metal restoration to a through tube in the penetration electrode formation approach of this invention operation gestalt -- it is a notching front view.

[Drawing 6] The example which actually formed the penetration electrode in the silicon substrate by the above-mentioned penetration electrode formation approach is shown, and it is the sketch of the microphotography of the cross section of the penetration electrode section of a silicon substrate.

[Drawing 7] It is the cross-sectional view of the layered product of a silicon IC chip (silicon substrate).

[Drawing 8] It is drawing in which showing other examples of this invention and showing chip size mounting of IC chip using INTAPOZA.

[Drawing 9] The sectional view of the image sensors which (A) shows the example of further others of this invention, and have a penetration electrode, and (B) are the sectional views showing the image sensors of a wire connection type.

[Drawing 10] It is the cross-sectional view of an optical circuit element (optical transmitter) in which the example of further others of this invention is shown, and the penetration electrode of a high aspect ratio was formed.

[Drawing 11] It is the typical sectional view of a penetration electrode section when a penetration electrode forms in a silicon substrate by the approach of of the conventional anisotropic etching and solder.

[Description of Notations]

10 Optical-Pumping Electrolytic-Polishing Equipment

11 Silicon Substrate

11a V type hollow

11b The front face of a silicon substrate

11c The rear face of a silicon substrate

12 Through Tube

13 Electrolytic Solution

14 Light Source

15 Cathode Electrode 21 Oxide Film

22 Impurity Diffused Layer (Shielding Layer)

23 Restoration Metal (the Same Sign Also Shows Molten Metal)

30 Metal Restoration Equipment

31 Vacuum Chamber

37 Vacuum Chamber for Buffers

34 Vacuum Aspirator

43 Molten-Metal Tub

44 Heater

70 Solder Ball

71 Silicon IC Chip

72 Penetration Electrode

73 Base Substrate

74 Solder Bump

80 Mother Board (Base Substrate)

81 INTAPOZA made from Silicon (Silicon Substrate)

82 Penetration Electrode

83 IC Chip

84 Electrode

85 Conductive Layer

86 Solder Ball

90 Image-Sensors Chip

91 Photoelectric Element Area (Active Region of Image Sensors)

92 Penetration Electrode

93 Silicon Substrate

94 Solder Ball

97 Conductive Layer

100 Platform made from Silicon (Silicon Substrate) 101A, 101B, 101C Penetration electrode

http://www4.ipdl.ncipi.go.jp/cgi-bin/tran\_web\_cgi\_ejje

### JP.2002-237468,A [DESCRIPTION OF DRAWINGS]

101 V Groove

101A, 101B Penetration electrode

101C Penetration electrode

102 Projected Part

102A Conductive layer

103 Surface Mounting Mold LD (Laser Diode)

104 Crevice of Reverse Trapezoidal Shape

104A Conductive layer

105 PD (Photo Diode)

106 Optical Fiber

107 Axial Center

109A, 109B Bonding wire (gold streak)

110 Electrode Pad

111 Solder Ball

[Translation done.]

# JPO and NCIPI are not responsible for any damages caused by the use of this translation.

This document has been translated by computer. So the translation may not reflect the original precisely.

\*\*\*\* shows the word which can not be translated.

In the drawings, any words are not translated.

[Drawing 2]

[<u>Drawing 4]</u> 11 01

[Drawing 6]

Ą

[Drawing 5]

http://www4.ipdl.ncipi.go.jp/cgi-bin/tran\_web\_cgi\_ejje

[Drawing 10]

## JP,2002-237468,A [DRAWINGS]

#### [Translation done.]

5/5 ペ

-ジ

# THIS PAGE BLANK (USPTO)

.

.

8

(12) 公開特許公報(A)

(11)特許出顧公開番号 特開2002-237468 (P2002-237468A)

(43)公開日 平成14年8月23日(2002.8.23)

| (51) Int.Cl.' | 識別記号    | FI   |        | 7 | 7]}*(参考) |

|---------------|---------|------|--------|---|----------|

| H01L          | 21/28   | HO1L | 21/28  | E | 4M104    |

|               | 21/02   |      | 21/02  | в | 5F043    |

|               | 21/3063 |      | 21/316 | S | 5F058    |

|               | 21/316  |      | 21/306 | L |          |

審査請求有 請求項の数4 OL (全 9 頁)

| (21)出願番号 | 特顧2001-34528(P2001-34528) | (71)出願人 | 000005186           |

|----------|---------------------------|---------|---------------------|

|          |                           |         | 株式会社フジクラ            |

| (22)出顧日  | 平成13年2月9日(2001.2.9)       |         | 東京都江東区木場1丁目5番1号     |

|          |                           | (72)発明者 | 淹沢 功                |

|          |                           |         | 東京都江東区木場1-5-1 株式会社フ |

|          |                           |         | ジクラ内                |

|          |                           | (72)発明者 | 佐藤(埠暢)              |

|          |                           |         | 東京都江東区木場1-5-1 株式会社フ |

|          |                           |         | ジクラ内                |

|          |                           | (74)代理人 | 100090549           |

|          |                           |         | 弁理士 加川 征彦           |

|          |                           |         |                     |

|          |                           |         | 最終頁に続く              |

(54)【発明の名称】 基板の貫通電極形成方法および貫通電極を有する基板

、(57)【要約】

【課題】 シリコン基板に高アスペクト比の貫通電極を 形成する。

【解決手段】 光励起電解研磨法によりシリコン基板1 1に高アスペクト比の貫通孔12を形成する。この貫通 孔12の内壁を酸化処理して絶縁層としての酸化膜21 を形成する。次いで、貫通孔12に溶融金属埋め戻し法 により金属23を充填して、貫通電極(23)とする。 シリコン基板11に高アスペクト比の貫通電極12を容 易に形成でき、例えばシリコン1Cチップを積層した高 密度実装の半導体パッケージを実現すること等が容易に なる。

21

h

【特許請求の範囲】

【請求項1】 シリコン基板等の基板に貫通電極を形成 する貫通電極形成方法であって、

1

光励起電解研磨法により、基板に高アスペクト比の貫通 孔を形成し、この貫通孔の内壁を酸化処理して絶縁層と しての酸化膜を形成し、次いで、前記貫通孔に溶融金属 埋め戻し法により金属を充填することを特徴とする基板 の貫通電極形成方法。

【請求項2】 貫通孔内壁に絶縁層としての酸化膜を形 成するに際して、貫通孔内壁に形成した酸化膜を一旦除 10 去し、その後再び貫通孔内壁を酸化処理して酸化膜を形 成する工程を少なくとも一回有することを特徴とする請 |求項1記載の基板の貫通電極形成方法。|

【請求項3】 貫通孔内壁に絶縁層としての酸化膜を形 成するに際して、貫通孔内壁に高濃度の不純物拡散を行 って、酸化膜の外側に不純物拡散層を形成することを特 徴とする請求項1記載の基板の貫通電極形成方法。

【請求項4】 貫通電極を有するシリコン等の基板であ って、

前記貫通電極は、光励起電解研磨法により形成され、内 20 壁に酸化膜を有する貫通孔と、前記貫通孔に充填された 金属よりなり、

前記貫通電極は前記基板内に少なくとも1カ所形成され ていることを特徴とする貫通電極を有する基板。

【発明の詳細な説明】

[0001]

【発明に属する技術分野】との発明は、シリコン基板等 の基板に貫通電極を形成する貫通電極形成方法と、当該 方法により形成された貫通電極を少なくとも1ヶ所有す る基板、および当該基板を用いたデバイスに関し、例え ば、シリコンICチップを積層して高密度実装する際の シリコン基板に貫通電極を形成する場合のように、高ア スペクト比の貫通電極を必要とする場合に好適に適用で きる基板の貫通電極形成方法と、貫通電極を有するシリ コン等の基板、および当該基板をベースにした電子デバ イスや光デバイスなどの各種デバイスに関する。 [0002]

【従来の技術】例えば、シリコン基板に表裏を貫通する 貫通電極を形成する方法としては、異方性エッチングを 行なった後、酸化膜を形成し、半田で導通を取る方法が 40 提案されている。この場合、図11に示すように、異方 性エッチングでシリコン基板1に形成した貫通孔2は、 基板厚さに対する開口部の面積が大きなものとなる。3 は酸化膜、4は半田を示す。また、シリコン基板に貫通 電極を形成する、ICP-RIE (Inductively Couple d Plasma - Reactive Ion Etching) 法を用いて貫通孔 を形成し、貫通孔内壁を金属メッキして貫通電極を形成 する方法も提案されてる。

【0003】一方、シリコン基板に高アスペクト比(孔 深さに対する開口部面積)の貫通孔を形成する技術とし 50 ば、シリコンICチップを積層して高密度実装する際の

て、光励起電解研磨法(J.Electrochem.Soc., Vol.137, No.2,pp653-659参照)が知られている。この光励起電解 研磨法の詳細は後述する。

[0004]

【発明が解決しようとする課題】上記従来の異方性エッ チング・半田の方法では、エッチング形状に制約があ り、シリコン基板1の厚さに対する貫通孔の開口部の面 積が大きくなるので、高アスペクト比の貫通電極を形成 することはできず、シリコンICチップの高密度実装を 行なおうとする場合における、シリコン基板への貫通電 極の形成には向かない。

【0005】また、ICP-RIE・金属メッキの方法 では、反応ガスやメッキ液が貫通孔内の奥深くまで進入 できないので、やはり、高アスペクト比の貫通電極を形 成することは困難である。

【0006】また、光励起電解研磨法により形成した貫 通孔の形状では、サイドブランチ等が生じるため平坦な 壁面が得られない。

【0007】本発明は上記事情に鑑みてなされたもの

で、高アスペクト比の貫通電極を形成することが可能で あり、また、貫通電極が形成される貫通孔の内壁を平坦 にできる基板の貫通電極形成方法および貫通電極を有す る基板を提供することを目的とする。

[0008]

30

【課題を解決するための手段】上記課題を解決する本発 明は、シリコン基板等の基板に貫通電極を形成する貫通 電極形成方法であって、基板に高アスペクト比の貫通孔 を形成し、この貫通孔の内壁を酸化処理して絶縁層とし ての酸化膜を形成し、次いで、前記貫通孔に溶融金属埋 め戻し法により金属を充填することを特徴とする。

【0009】請求項2は、請求項1の基板の貫通電極形 成方法において、貫通孔内壁に絶縁層としての酸化膜を 形成するに際して、貫通孔内壁に形成した酸化膜を一旦 除去し、その後再び貫通孔内壁を酸化処理して酸化膜を 形成することを特徴とする。

【0010】請求項3は、請求項1の基板の貫通電極形 成方法において、貫通孔内壁に絶縁層としての酸化膜を 形成するに際して、貫通孔内壁に高濃度の不純物拡散を 行って、酸化膜の外側に不純物拡散層を形成するととを 特徴とする。

【0011】請求項4は、貫通電極を有するシリコン等 の基板であって、前記貫通電極は、光励起電解研磨法に より形成され、内壁に酸化膜を有する貫通孔と、前記貫 通孔に充填された金属よりなり、前記貫通電極は前記基 板内に少なくとも1カ所形成されている貫通電極を有す る基板を特徴とする。

[0012]

【発明の実施の形態】以下、本発明の実施の形態を図1 ~図10を参照して説明する。との実施形態は、例え

10

20

3

シリコン基板に貫通電極を形成する場合を想定してい る。

①まず、図1(イ)に示すように、シリコン基板11 に、KOH等のエッチング液を用いた異方性エッチング によりV形凹所(この例は四角錐状の凹所)11aを形 成する。

【0013】 ②次いで、前記シリコン基板11のV形凹 所11aの位置に、光励起電解研磨法により図1(ロ) のように貫通孔12を形成する。光励起電解研磨法によ る貫通孔12の形成の原理を図2に示した光励起電解研 磨装置10および図3を参照して説明する。前記のよう に表面11bに予めKOHによりV形凹所11aを形成 したn型のシリコン基板11を、電解槽18内のHF溶 液からなる電解液13に浸漬し、このシリコン基板11 の前記V形凹所11aに対応する裏面11cに赤外線フ ィルタ17を通して光(光源を14で示す)を照射しつ つ、陽極とした前記シリコン基板11と陰極電極15と の間に電流(直流電源を16で示す)を流すと、シリコ ン基板11の前記V形凹所位置が選択的にエッチングさ れ、このV形凹所位置に貫通孔12が形成される。選択 的にエッチングされる原理を説明すると、図3に示すよ うに、n型のシリコン基板2の裏面に光14aを照射す ると、その光照射による励起でシリコン基板2の裏面で 少数キャリア(正孔)が生成され、その少数キャリアが 表面側の四角錐状のV形凹所11aの先端に集中すると とにより、V形凹所11aの先端のみが電気化学的にエ ッチングされ、そのエッチングが進行して貫通孔が形成 される。この光励起電解研磨法による貫通孔12の形成 の具体的な実施例としては、例えば、50℃、2.5w t%のHFエッチング液中にて、光の照度6mW/c、 m<sup>2</sup>、印加電流0.1mA、印加時間24時間で研磨を 行い、例えば直径15μm、深さ400μmの貫通孔を 形成する。

【0014】次いで、前記貫通孔12の内壁を酸化し て、図1(ハ)に示すように、絶縁層としての酸化膜2 1を形成する。酸化膜21の形成は、例えば熱酸化法に より形成することができる。熱酸化の具体的な実施例と しては、例えば、1100℃、2000cc/min.のスチ ームを流したウェット雰囲気に3時間曝して、酸化膜2 1を形成する。

【0015】なお、絶縁層として酸化膜21を形成する 場合、光励起電解研磨法で設けた貫通孔の内壁はサイド ブランチ等が生じて平坦な内壁面が得られないので、一 旦形成した酸化膜21を除去し、再度酸化して酸化膜を 形成することが望ましい。これにより、貫通孔12の内 壁面を平坦化でき、良好な貫通電極を形成できる。な お、酸化膜除去は、BOE (バッファードフッ酸)等に より貫通孔12内の酸化膜を選択的にエッチングするこ とで行うことができる。また、場合によっては、前記酸 化膜除去と酸化膜再形成の工程を複数回繰り返すと、貫 4

通孔12の内壁面を一層平坦化することができる。 【0016】また、酸化膜を形成する際に、高濃度の不 純物拡散を行い、それによって形成される層(不純物拡 **散槽)をシールド層として用いることができる。図4**に 不純物拡散により形成した不純物拡散層を22で示す。 シールド層の形成により、ノイズを抑制できる。拡散さ せる不純物としては、例えば、n型シリコン基板の場 合、ボロン等のp型層を形成する物質を拡散させるとよ い。また、不純物拡散は例えば熱拡散法により行なうこ とができる。この熱拡散法によれば、不純物拡散層22 の上の絶縁層(酸化膜21)の形成も同時に行なうこと ができるので、能率的である。熱拡散による不純物拡散 の具体的な実施例としては、例えばn型シリコン基板に ボロンを拡散する場合、固相ないしは気相の不純源を用 い、950℃、1時間、窒素雰囲気でボロンガラスをデ ボジションした後、1,100℃、ウェット酸化雰囲 気、3時間ドライブインを行うと、例えば、2μm程度 の高濃度P++層(不純物拡散層22)が形成される。 【0017】次いで、溶融金属埋め戻し法により、図1 (ニ) に示すように貫通孔12内に金属23を充填す

る。溶融金属埋め戻し法とは、被加工対象となるシリコ ン基板(ワーク)に形成された微細孔などの微細空間に 金属を充填する方法であって、まず、金属を充填しよう とするワークの雰囲気圧を減圧し、次いで減圧状態を保 ったまま、前記ワークを溶融金属に挿入し、次いで前記 溶融金属の雰囲気圧を加圧して、金属挿入前後における 雰囲気圧差により前記空間に溶融金属を充填し、次いで ワークを溶融金属槽から引き上げて冷やすことを特徴と する方法である。ここで、充填する金属としては、イン 30 ジウム(In)、スズ(Sn)、あるいは金-錫の共晶 半田など比較的融点が低く、蒸気圧の低い金属を用いる とよいが、特にそれらに限定されない。この溶融金属埋 め戻しの具体的な実施例としては、例えば図5のような 溶融金属充填装置30を使用して、例えば10<sup>-</sup><sup>3</sup>Pa (パスカル)程度の減圧雰囲気中で、貫通孔12をあけ たシリコン基板11をワークとして、例えば300℃の 溶融すずに浸漬し、その後、大気圧下に雰囲気を戻すこ とで高アスペクト比の貫通孔12内に錫を充填させる。 【0018】前記溶融金属充填装置30は、ヒータ44 40 付きの溶融金属槽43を配置した真空チャンバー31

(1) そのは、していたいでは、

(1) そのは、

(2) くれにシャッター35で開閉可能な開口部36で連通するバッファ用真空チャンバー37とを持ち、シリコン基板11を把持するワーク固定用アーム47を蓋50

(2) ないのり付けている。両チャンバー31、37は、真空ボンブ装置34に吸引管33または真空粗引き用吸引管38を介して接続され、また、図示略の窒素ボンベに窒素導入管39、40を介して接続されている。

(0019)上記の金属充填装置30でシリコン基板1100貫通孔12に金属を充填する作業手順を説明する

化膜除去と酸化膜再形成の工程を複数回繰り返すと、貫 50 と、蓋50を閉じワーク固定用アーム47で把持したシ

10

40

リコン基板11をバッファ用真空チャンバー37内に位 置させた状態で、バッファ用真空チャンバー37内部を 真空ボンブ装置34により真空粗引きする。次いで、シ ャッター35を開く(なお、真空チャンバー31は先に 減圧しておく)。次いで、真空ボンプ装置34で、真空 チャンパー11およびバッファ用真空チャンパー17の 内部を真空吸引し、真空圧10-°~10-° Pa程度ま で減圧する。次いで、ヒータ44で加熱して溶融金属槽 43内の金属を溶融させ、溶融金属23内にシリコン基 板11を挿入する。シリコン基板11が溶融金属23と 同じ温度に達した後、真空チャンバー11およびバッフ ァ用真空チャンバー17内に窒素ボンベからの窒素を導 入して、内部を2~5×10<sup>5</sup> Pa (2~5 kgf/cm<sup>2</sup>)程度 まで加圧する。この加圧により、溶融金属23が高アス ペクト比の貫通孔12内に充填される。その後、シリコ ン基板11を溶融金属槽43から引き上げ、真空チャン バー31の外に取り出して、室温にて空冷する。これに より、シリコン基板11の貫通孔12への金属充填作業 が終了する。

【0020】なお、貫通孔12の内壁面に絶縁層(酸化 20 膜)を形成する方法としては、前述の熱酸化法に限ら ず、例えばSiO<sub>2</sub>系皮膜形成用塗布液等の液相によ り、低温条件下で形成することも考えられる。この方法 は、既にシリコン基板11上に回路等が形成されている 場合、それらに熱による影響を及ぼさないので、有利に なる。

【0021】本発明は、シリコンICチップの積層高密 度実装(3次元実装)に適用して好適である。図7は、 シリコンICチップ(シリコン基板)の積層体を示す横断 面図である。図中71は、光励起電解研磨法により2箇 30 所の貫通電極72が形成されたシリコンICチップであ り、該シリコンICチップ71は、ベース基板73上に、 上下の位置を合わせて3枚積層されている。シリコンIC チップ71は、例えば、同一ウエハから切り出された同 一回路パターンを有し、ウエハ表面から見た場合におい て、各チップ内の同一位置に貫通電極72と回路パター ン(図示せず)が形成され、これらの貫通電極72は、 上下端を合わせて接続されている。すなはち、電極下端 に設けられた半田バンプ74と、相手側チップ上の貫通 電極上端が接続され、これらチップの貫通電極72は、 シリコン製ベース基板73に形成された貫通電極72と 位置合わせ接続される。この結果、ベース基板とシリコ ンICチップを貫通する共通電極が形成され、該共通電極 の下端の半田ボール70は、図示しないベース基板の配 線回路と接続される。ただし、敢えて貫通電極の上下位 置を揃えないような設計をする場合には、一方のチップ 下部の半田バンプを、他方のチップ上部の配線パターン (貫通電極と導通する他方のチップ上に形成された電極 層)と接続する事も可能である。以上のように、高アス ペクト比の貫通電極が形成された何枚かのICチップを任 50 意位置に位置決めして重ね合わせ接続することにより、 複数層に積み上げられ実装密度の向上した3次元ICデバ イスを作ることが可能である。なお、貫通電極の数は2 本には限定されず、これは他の実施例においても同様で ある。

6

【0022】図8は、本発明の他の実施例であり、イン ターボーザを用いたICチップのチップサイズ実装を示 す。図中81は、光励起電解研磨法により形成された2 ヶ所の貫通電極82を有するシリコン製のインターボー ザ(シリコン基板)あり、該インターボーザ上には、例 えばフェースダウンされたICチッブ83が搭載されてい る。ICチップ表面の電極84は、インタボーザ表面の導 電層85を介して貫通電極82へ接続され、該インター

ポーザ下面においては、貫通電極82下端に形成された 半田ボール86が、マザーボード(ベース基板)80ト の配線パターンと接続されている。従来、インタポーザ を用いたチップ実装では、マザーボードとの接続に制約 が多く、配線密度にも限界があったが、本実施例では、 高アスペクト比の貫通電極を複数形成することにより、

インタボーザの配線パターン設計の制約が少なくなり、 実装構造(あるいはパッケージ構造)を簡略化すること ができる。さらに、インターボーザの素材としてシリコ ンを用いているため、ICチップと熱膨張係数の整合性が 良好になり、他のセラミック製のものに比較して、マザ ーボードへ実装する際にチップが受ける熱応力歪みが少 なく、また、シリコンの熱伝達効率が比較的優れている ため、チップの発生熱を逃がし易いという利点が得られ る。さらに、一般に普及しているシリコン精密加工技術 が使えるため表面配線パターンの精密化が可能という利 点も得られる。

[0023]図9(A)は、本発明の他の実施例であ り、貫通電極を有するイメージセンサを示す。図中、9 1はイメージセンサチップ90内の光電素子エリアであ り、92は光励起電解研磨法によりシリコン基板93に 形成された高アスペクト比の貫通電極である。該貫通電 極92は、イメージセンサの能動領域(光電変換素子が 形成された光電素子エリア)91の外側でチップ端部に 形成され、その上端がチップ表面の電極層を介して能動 領域91へ接続されている。また、下端は半田ボール9 4等を介して図示しないマザーボード表面の配線バター

ンと接続されている。

【0024】図9(B)は、ワイヤ接続方式のイメージセ ンサを示す。本図では、イメージセンサはチップの素子 エリアと同一面に、該素子エリアに導通する比較的面積 の大きなワイヤボンドパッド95を形成し、ボンディン グワイヤ96により外部のリードフレーム等と接続して いる。また、金線(ワイヤ)接続時に発生する熱等の影 響を軽減するため、ワイヤボンドパッドとイメージエリ アは有る程度離隔する必要があり、以上の理由から、チ ップ表面に占めるイメージエリアの面積には制約があ

る。 【0025】とれに対して、本発明では、高アスペクト 比の貫通電極上端が、導電層97を介して光電素子エリ ア91と接続されており、貫通電極下端の半田ボール9 4により外部と接続されるから、イメージエリアと同一 面へのワイヤボンディングパッドが不要となる。従っ て、イメージセンサのチップ面積に占める素子エリアを 大きくすることができるから、イメージセンサを小型 化、あるいは限られた大きさのチップ内に広い面積の素 子エリアを確保することができる。また、ワイヤボンデ 10 ィングが不要であるから、ベース基板への表面実装が容 易となりイメージチップ実装基板の小型と薄型化、並び に製造コストの削減を計ることができる。 【0026】図10は、本発明の他の実施例であり、高 アスペクト比の貫通電極が形成された光回路素子(光ト ランスミッタ)の横断面図を示す。図中100は、光励 起電解研磨法により形成された4ヶ所の貫通電極101 A 101B、101C(他の1ヶ所は図示せず)を有す る精密加工されたシリコン製のプラットフォーム(シリ コン基板)、101は、光ファイバ106を位置決め固 20 定するV溝、102は面実装型LD(レーザダイオード) 103の一方の電極面が接続される頂面が導電層102 Aをなす断面台形状の突部、104はモニタ用PD(ホト ダイオード)105の片側電極面に接続される凹底部が 導電層104Aをなす逆台形状の凹部である。該突部1 02と該凹部104の下部には、導電層102A、導電 層104Aと導通する貫通電極101Aと101Bが形成 され、これら貫通電極101A、101Bの下端部は半田 バンプ(パッド)を形成して、図示せぬ外部回路と接続 される。一方、他の2ヶ所の貫通電極101C(1ヶ所 は図示せず)は、プラットフォーム表面100A上の2 ヶ所の電極パッド110(1ヶ所は図示せず)に接続さ れ、これら電極パッドから導出する2本のボンディング ワイヤ(金線)109A、109BがLD103、PD105 の他の片側電極面に接続される。更に具体的には、金線 109AはLD103上の片側電極に直接ボンディングさ れ、金線109Bは素子電極に直接接続されるのではな く、ブラットフォーム上にメッキされた導電層104Aの延

7

出部と接続される。プラットフォーム100の下部で は、これら貫通電極の下端が半田ボール111などを介 40 して実装基板に表面実装される。

【0027】次に、これら光デバイスの並び方向は、光 ファイバ106の軸心107と一致するように光軸が合 わされており、LD103の出射光が光ファイバへ入射 し、PD105がLD出力をモニタする。この実施例によれ は、光素子下部の各導電層102A 104Aが貫通電極 101A、101Bを介して外部回路と導通しているため に、ブラットフォーム表面上の配線パターンの形成が簡 略化される。また、ワイヤ(金線)ボンディングは、ブ ラットフォーム内の電極パッド110から光素子間だけ 8

であるから、光素子と外部リードフレームを接続するの に比較してワイヤ長が短くなり接続が容易となる。従っ て、光デバイス全体が小型化するのみならず、接続工数 を経らすことができるため製品コストを低下させること ができる利点がある。なお、上記フラットフォームの形 状を変更して、光ファイバからの外部入射光を受光用PD で受けるような構成とすれば、光レシーバを構成するこ とができる。また、光ファイバを2本(v溝を2本)と して、ブラットフォームを加工して同一ブラットフォー ム上に、光トランスミッタと光レシーバを作り付けれ

[0028]以上説明したように、本発明は、高アスペ クト比の貫通電極を各種素子に形成することができ、ま た、汎用的なシリコン精密加工技術の利用が可能である から、各種素子、デバイスの精密化、小型化、ならびに 実装密度の向上を計ることができる。また、煩雑でコス ト高となるワイヤボンド等の工程を省略できるから、製 品コストを低下させることも可能となる。なお、本発明 はシリコン基板に貫通電極を形成する場合が主である

ば、光トランシーバが構成できる。

) が、シリコン以外の素材による基板に貫通電極を形成す ることも考えられる。

[0029]

【発明の効果】本発明によれば、例えば光励起電解研磨 法により基板に高アスペクト比の貫通孔を形成し、この 貫通孔の内壁を酸化処理して絶縁層としての酸化膜を形 成し、次いで、前記貫通孔に溶融金属埋め戻し法により 金属を充填して、貫通電極を形成するので、高アスペク ト比の貫通電極を容易に得ることができる。これによ

り、例えばシリコンICチップを積層した高密度実装の 30 半導体バッケージや光デバイスを実現すること等が容易 になる。

[0030]請求項2のように、貫通孔内壁に形成した 酸化膜を一旦除去した後、再酸化して酸化膜を形成すれ ば、貫通孔内壁を平坦化することができ、良好な貫通電 極を形成できる。

【0031】請求項3のように、貫通孔内壁に高濃度の 不純物拡散を行って、酸化膜の外側に不純物拡散層を形 成すれば、この不純物拡散層をシールド層として利用で き、ノイズの抑制に有効である。

【図面の簡単な説明】

【図1】本発明の一実施形態の基板の貫通電極形成方法 を工程に分けて説明する模式図であり、(イ)はシリコ ン基板にV形凹所を形成した段階、(ロ)は光励起電解 研磨法で貫通孔をあけた段階、(ハ)は貫通孔内壁に酸 化膜を形成した段階、(ニ)は貫通孔に金属を充填して 貫通電極を形成した段階を示す。

【図2】本発明実施形態の貫通電極形成方法において、 貫通孔の形成に用いる光励起電解研磨装置の模式図であ る。

50 【図3】上記の光励起電解研磨法で、V形凹所に選択的

特開2002-237468

10

9 なエッチングが行なわれる原理を説明する図である。 【図4】図1(ハ)の酸化膜の形成に際して、不純物拡 散を行なってシールド層(不純物拡散)を形成した状態 を示す模式図である。 【図5】本発明実施形態の貫通電極形成方法において、 貫通孔への金属充填に用いる金属充填装置の要部の一部 切り欠き正面図である。 【図6】上述の貫通電極形成方法で実際にシリコン基板 に貫通電極を形成した実施例を示すもので、シリコン基 板の貫通電極部分の断面の顕微鏡写真のスケッチであ 10 る。 【図7】シリコン1Cチップ(シリコン基板)の積層体 の横断面図である。 【図8】本発明の他の実施例を示すもので、インターポ ーザを用いたICチップのチップサイズ実装を示す図で ある。 【図9】(A)は本発明のさらに他の実施例を示すもの で、貫通電極を有するイメージセンサの断面図、(B) はワイヤ接続方式のイメージセンサを示す断面図であ る。 20 【図10】本発明のさらに他の実施例を示すもので、高 アスペクト比の貫通電極が形成された光回路素子(光ト ランスミッタ)の横断面図である。 【図11】従来の異方性エッチング・半田の方法でシリ コン基板に貫通電極の形成した場合における貫通電極部 分の模式的な断面図である。 【符号の説明】 10 光励起電解研磨装置 11 シリコン基板 lla V形凹所 30 11b シリコン基板の表面 11c シリコン基板の裏面 12 貫通孔 13 電解液 14 光源 15 陰極電極 21 酸化膜 22 不純物拡散層(シールド層) 23 充填金属(溶融金属も同じ符号で示す) **≭**⊿∩

30 金属充填装置

| * | 31  | 夏空チャンバー                        |

|---|-----|--------------------------------|

|   | 37  | バッファ用真空チャンバー                   |

|   | 34  | 真空吸引装置                         |

|   | 43  | 溶融金属槽                          |

|   | 44  | ヒータ                            |

|   | 70  | 半田ボール                          |

|   |     | シリコンICチップ                      |

|   |     | 貫通電極                           |

|   | 73  | ベース基板                          |

| 0 | 74  | 半田バンプ                          |

|   |     | マザーボード(ベース基板)                  |

|   |     | シリコン製のインターボーザ(シリコン基板)          |

|   |     | 貫通電極                           |

|   |     | ICチップ                          |

|   | 84  | 電極                             |

|   |     | 導電層                            |

|   |     | 半田ボール                          |

|   |     | イメージセンサチップ                     |

| _ |     | 光電素子エリア(イメージセンサの能動領域)          |

| 0 |     | 貫通電極                           |

|   |     | シリコン基板                         |

|   |     | 半田ボール                          |

|   |     | - 導電層<br> シリコン製のブラットフォーム(シリコン基 |

|   | 板)  | シリコン製のフラットフォーム(シリコン華           |

|   |     | A、101B、101C 貫通電極               |

|   |     |                                |

|   |     | A、101B 貫通電極                    |

|   |     |                                |

| D |     | · 突部                           |

| - |     | A<br>導電層                       |

|   |     | 面実装型LD(レーザーダイオード)              |

|   | 104 |                                |

|   | 104 | A 導電層                          |

|   | 105 | PD(ホトダイオード)                    |

|   | 106 | 光ファイバ                          |

|   | 107 |                                |

|   | 109 | A、109B ボンディングワイヤ(金線)           |

|   | 110 | 電極パッド                          |

| C | 111 | 半田ボール                          |

【図1】

【図2】

【図6】

۲.

【図11】

(7)

8

【図5】

【図10】

フロントページの続き

(72)発明者 末益 龍夫

東京都江東区木場1-5-1 株式会社フジクラ内

(72)発明者 糸井 和久

東京都江東区木場1-5-1 株式会社フジクラ内

Fターム(参考) 4M104 AA01 BB09 BB36 CC01 DD07 DD09 DD22 DD23 DD26 DD31 EE02 EE16 FF01 FF21 GG04 GC05 HH14

1

5F043 AA02 BB02 DD08 DD14 FF04. FF06 GG04

- 5F058 BC03 BE04 BE10 BF46 BF56 BF63 BJ10

- . ...

ř.

# THIS PAGE BLANK (USPTO)

L